## A Ku-Band Ultra Super Low-noise Pseudomorphic Heterojunction FET in a Hollow Plastic PKG

T. Hirokawa, H. Negishi\*, Y. Nishimura\*, S. Ichikawa, J. Tanaka, T. Kimura, K. Watanabe, and Y. Nashimoto\*

Compound Semiconductor Device Division, NEC Corporation

1753, Shimonumabe, Nakahara-ku, Kawasaki, 211, Japan

\*ULSI Device Development Laboratories, NEC Corporation

2-9-1, Seiran, Otsu, Shiga, 520, Japan

### Abstract

This paper reports Ku-band ultra super low-noise pseudomorphic heterojunction FETs (pHJFETs) in a newly developed hollow plastic package. To achieve higher performance of pHJFETs, we employed further optimized epi-layer structure with good interfacial quality. The developed packaged HJFETs with 0.17  $\mu$ m T-shaped gate exhibited extremely low noise performance of 0.35 dB typical noise figure with 12.5 dB associated gain at 12 GHz.

In this paper, we report super low-noise pHJFETs with a sharp interfacial atomic profile AlGaAs/InGaAs epi-layer grown by MBE under the optimized growth conditions. The devices have a T-shaped gate with a very short footprint length (0.17  $\mu$ m), and exhibited typical noise figure of 0.35 dB with 12.5 dB associated gain at 12 GHz. Furthermore, a hollow plastic package has been newly developed, and has been shown to be effective in achieving high performance as well as low cost.

### I Introduction

Over the past several years, low noise performance of pHJFETs has been drastically improved[1-3]. To make further improvement in RF performance, HJFETs have been fabricated with shorter gate length. In accordance with increasing demand for very short gate length fabrication, it is inevitable to employ further optimized epi-layer structure with good interfacial quality.

To get the larger conduction-band discontinuities in the channel, several efforts have been made to increase the In composition of the channel[4-5]. As the segregation effects of In atoms during growth by molecular-beam epitaxy (MBE) cause composition gradation at the AlGaAs/InGaAs interface, several modified growth conditions have been proposed to improve the compositional abruptness of interfaces with InGaAs[6-7]. Recently, the dependence of pHJFET performances on In content with depth have been investigated. It is suggested that the performance of pHJFETs is most enhanced by a relatively high In content near the bottom of the quantum well[8].

### II Device Fabrication

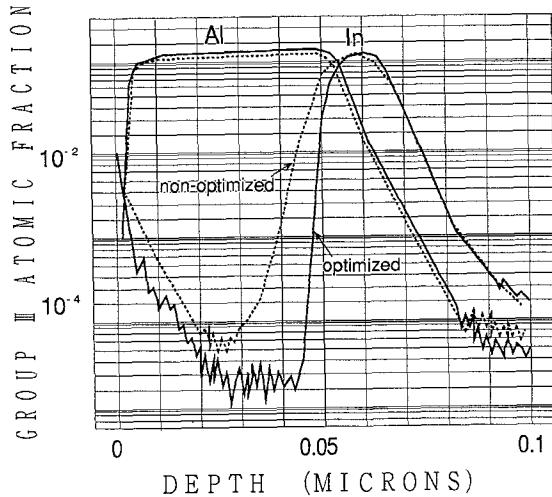

The epi-layers were grown by MBE on (100) 3-inch semi-insulating GaAs substrates. The FET layers consist of i-GaAs buffer layer, 15 nm i-InGaAs channel layer, 40 nm donor AlGaAs layer with a density of  $2 \times 10^{18} \text{ cm}^{-3}$  and 80 nm cap GaAs layer with a density of  $3 \times 10^{18} \text{ cm}^{-3}$ . To improve the abruptness of the AlGaAs/InGaAs interface, we have successfully reduced In surface segregation using low substrate temperature and thermal desorption of the excess In during a growth interruption at the end of the InGaAs layer [9][10]. For comparison, the epi-layers without a growth interruption (non-optimized epi-layers) have also been prepared. SIMS depth profile for the improved AlGaAs/InGaAs epi-layer is shown in Fig. 1. The results indicate that In surface segregation at the AlGaAs/InGaAs interface is effectively suppressed. The measured sheet carrier concentration and the electron Hall mobility of the epitaxial wafers for the developed HJFETs are given in Table 1. The electron mobility obtained for the optimized channel layer is  $25,000 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$  at 77 K, which is much higher

TH

3F

Fig.1 The results of SIMS In, Al depth profiling analysis.

Table 1 The measured the electron Hall mobility and sheet carrier concentration data at 77K.

| channel                     | electron Hall mobility( $\text{cm}^2 \text{V}^{-1} \text{s}^{-1}$ ) | sheet carrier concentration ( $\text{cm}^{-2}$ ) |

|-----------------------------|---------------------------------------------------------------------|--------------------------------------------------|

| optimized channel layer     | 25,000                                                              | $1.6 \times 10^{12}$                             |

| non-optimized channel layer | 13,000                                                              | $2.0 \times 10^{12}$                             |

than that obtained for the non-optimized channel layer.

The developed HJFETs have 4 gate fingers. T-shaped gates were fabricated by electron-beam evaporation and a lift-off technique employing direct-write electron-beam lithography [11]. The gate length and the total gate width are 0.17  $\mu\text{m}$  and 200  $\mu\text{m}$ , respectively. The 4-finger gate device has the airbridged-drain structure to reduce the parasitic gate-source capacitance.

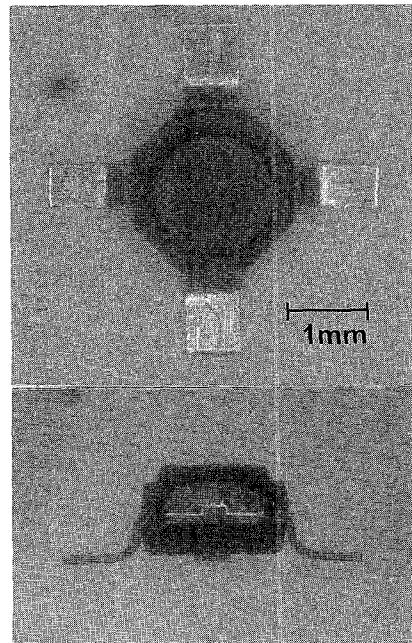

The HJFETs were assembled in plastic packages with a hallow structure, which has been newly developed for use in high frequency application. The cross section of the new hollow plastic package is shown Fig. 2. The plastic package consists of the lead frame embedded on the surface of the plastic platform, the bank on the outside of plastic platform to get enough lead strength and the plastic cap adhered on the bank so as to seal the chip in the package. The plastic package size is 2 mm across, 1.45 mm thick and 4 mm long containing the lead-length.

Fig.2 Top and cross-sectional view of a developed hollow plastic package.

### III Device Performance

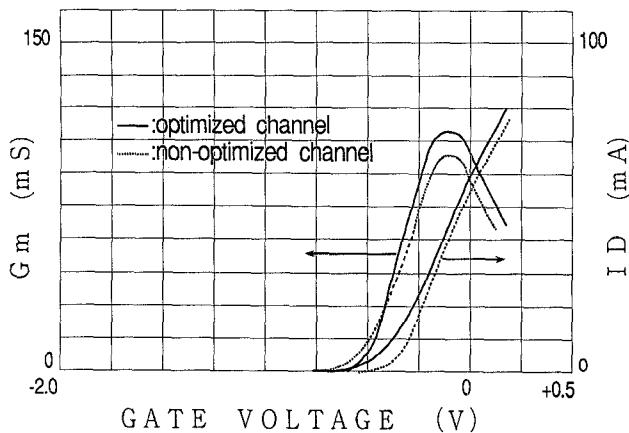

Figure 3 shows gate bias dependence of the measured transconductance for the optimized channel HJFET's at a drain voltage of 2.0 V. The device exhibits a peak transconductance of 535 mS/mm and good pinch-off characteristics. The results for the non-optimized channel devices are also plotted in Fig. 3. A 10 percent improvement in extrinsic  $gm$  is obtained for the optimized channel HJFET. The superior  $gm$  characteristics are considered to be due to the mobility improvement in electron transport properties for the effective prevention of the In segregation at the AlGaAs/InGaAs interface.

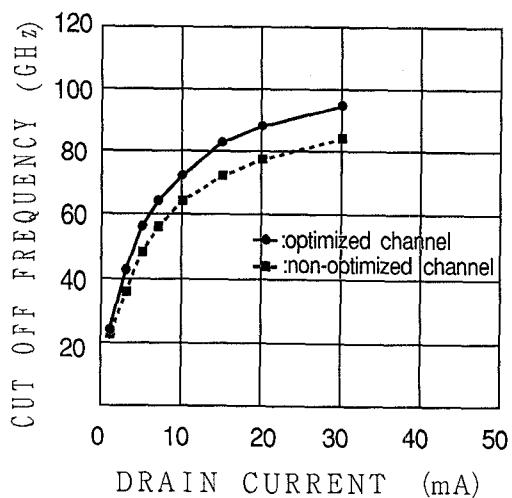

On-wafer device S-parameter measurements have been performed in the frequency range from 50 MHz to 40 GHz by using a Cascade Microtech microwave probe station and Wiltron360 network analyzer. The cut-off frequency  $f_T$  as a function of drain current for the devices, obtained by extrapolating the current gain  $H21$  at -6 dB/octave, are shown Fig.4. The device with the optimized channel shows higher cut-off frequencies than those for the non-optimized channel device over the whole drain current range investigated.

Fig.3 The transconductance  $g_m$  and the drain current  $I_D$  as a function of the gate voltage measured at a drain voltage  $V_D$  of 2.0V.

Fig.4 The cut-off frequency  $f_T$  as a junction of drain current for the devices at a drain voltage  $V_D$  of 2.0V.

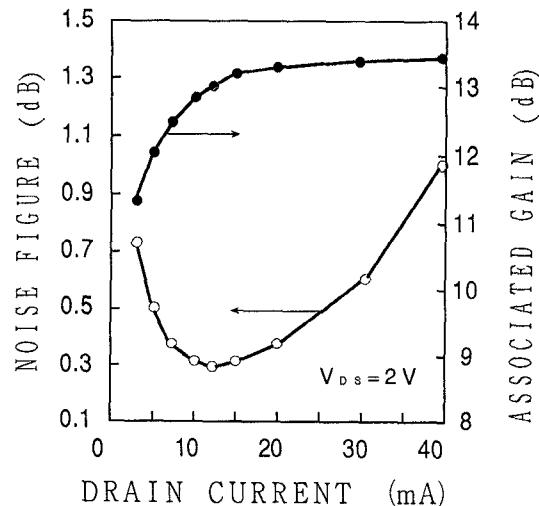

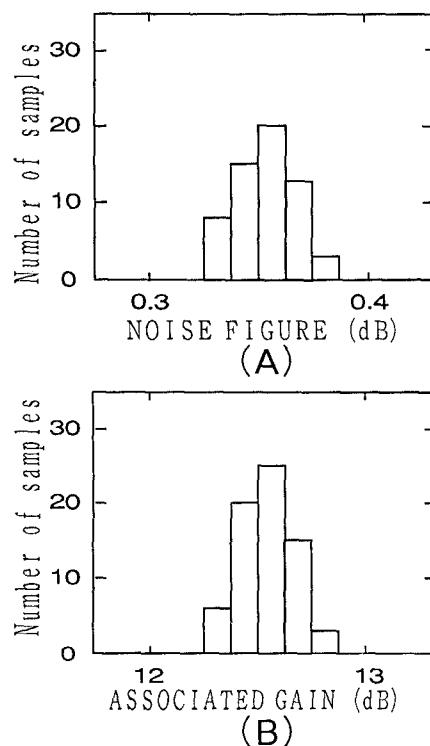

The noise performance for the plastic packaged HJFETs was evaluated at 12 GHz. The drain current dependence of the noise figure and the associated gain at 12 GHz are shown in Fig. 5. The minimum noise figure of 0.31 dB with the associated gain of 12.9 dB was obtained at a drain current of 12 mA. Fig. 6 shows the distribution of noise figure and associated gain at 12 GHz at 2 V drain voltage and 10 mA drain current. The average noise figure is 0.35 dB with the average associated gain of 12.5 dB. These RF characteristics for the HJFET's in the plastic packages are almost the same as those for the HJFET's in conventional ceramic packages.

Fig.5 The drain current dependences of the noise figure and associated gain at 12GHz.

Fig.6 Distribution of noise figure (A) and associated gain (B) at a drain current  $I_D$  of 10mA and drain voltage  $V_D$  of 2.0V.

The equivalent circuit parameters of the packaged HJFETs are summarized in Table 2. The device was biased at a drain voltage of 2 V and a drain current of 10 mA. The parasitic capacitance between the gate and ground lead was obtained of 0.03 pF, which is enough small compared to conventional transfer molded plastic packages.

Table 2 The equivalent circuit parameters for the packaged HJFET obtained by S-parameter measurements.

| Parameter (chip) | Value        | Parameter (package) | Value          |

|------------------|--------------|---------------------|----------------|

| gm               | 75mS         | Lg                  | 0.29nH         |

| gd               | 5.9mS        | Ld                  | 0.48nH         |

| Cgs              | 0.15pF       | Ls                  | 0.06nH         |

| Cdg              | 0.03pF       | Cg                  | 0.03pF         |

| Cds              | 0.07pF       | Cd                  | 0.05pF         |

| Ri               | 4 $\Omega$   | Rg                  | 0.065 $\Omega$ |

| Rs               | 1.9 $\Omega$ | Rd                  | 0.065 $\Omega$ |

| Rd               | 2.1 $\Omega$ |                     |                |

| Rg               | 1.0 $\Omega$ |                     |                |

#### IV Conclusion

Super-low noise HJFET's with an optimized epi-layer structure has been newly developed. The developed HJFET's showed higher cut-off frequencies compared to non-optimized channel FET. Extremely low noise performance has been achieved for the newly developed plastic packaged pseudomorphic HJFETs with 0.17  $\mu\text{m}$  T-shaped gate. Typical noise figure of 0.35 dB with 12.5 dB associated gain has been obtained at 12 GHz. These HJFETs in the plastic package are promising for future wide application area.

#### Acknowledgment

The authors would like to thank Dr. T. Itoh and K. Ueda for their valuable discussions. The authors also would like to thank Y. Tedo, Y. Shouji, Y. Takashima and K. Maeyama for the device fabrication, H. Yonehara for micro-wave measurements. They are also grateful to T. Noguchi and Dr. A. Higashisaka for their continuous support and encouragement throughout this work.

#### REFERENCE

1. L. D. Nguyen, et al., "Charge Control, DC, and RF Performance of a 0.35  $\mu\text{m}$  Pseudomorphic AlGaAs/InGaAs Modulation-Doped Field-Effect Transistor," IEEE Trans. Electron Devices, ED-35, pp. 139, 1988.

2. P. Chao, et al., "DC and Microwave Characteristics of Sub-0.1- $\mu\text{m}$  Gate-Length Planar-Doped Pseudomorphic HEMT's," IEEE Trans. Electron Devices, ED-36, pp. 461, 1989.

3. K. L. Tan, et al., "60-GHz Pseudomorphic  $\text{Al}_{0.25}\text{Ga}_{0.75}\text{As}/\text{In}_{0.28}\text{Ga}_{0.72}\text{As}$  Low-Noise HEMT's," IEEE Electron Device Lett., 12, pp. 23, 1991.

4. L. D. Nguyen, et al., "0.2- $\mu\text{m}$  Gate-Length Atomic-Planar Doped Pseudomorphic  $\text{Al}_{0.3}\text{Ga}_{0.7}\text{As}/\text{In}_{0.25}\text{Ga}_{0.75}\text{As}$  MODFET's with  $f_T$  over 120GHz," IEEE Electron Device Lett., 9, pp. 374, 1988.

5. K. Onda, et al., "Dc and Microwave Performances of (InAs)GaAs Short Period Superlattice Channel 2DEGFET's," IEICE Trans., E 74, pp. 4114, 1991.

6. J. M. Moison, et al., "Surface segregation of third-column atoms in group III - V arsenide compounds: Ternary alloys and heterostructures," Phys. Rev., B, 40, pp. 6149, 1989.

7. R. Kaspi, et al., "Improved compositional abruptness at the InGaAs on GaAs interface by presaturation with In during molecular-beam epitaxy," Appl. Phys. Lett., 67, pp. 819, 1995.

8. D. C. Look, et al., "Effects of In profile on material and device properties of AlGaAs/InGaAs/GaAs high electron mobility transistors," J. Appl. Phys., 79(1), pp. 540, 1996.

9. K. R. Evans, et al., "Surface chemistry evolution during molecular beam epitaxy growth of InGaAs," J. Vac. Sci. Technol., B, 13(4), pp. 1820, 1995.

10. H. Toyoshima, et al., "In surface segregation and growth-mode transition during InGaAs growth by molecular-beam epitaxy," Appl. Phys. Lett. 63(6), pp. 821, 1993.

11. N. Samoto, et al., "A Novel Electron-Beam Exposure Technique for 0.1- $\mu\text{m}$  T-Shaped Gate Fabrication," J. Vac. Sci. Technol., B8, 6, pp. 1335, 1990.